# High-Performance NED Nuclear Event Detector

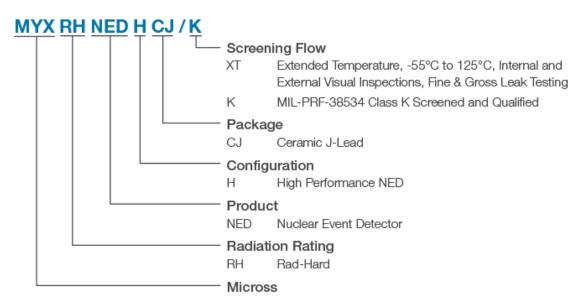

Part Number: MYXRHNEDHCJ/XT, MYXRHNEDHCJ/K

## **Preliminary Data Sheet**

Micross' High-Performance NED features a 4X increase in radiation dose rate sensitivity and 25% faster response times at 5X lower overdrive levels relative to legacy devices, with integrated differential drivers providing SWaP reduction, improved noise immunity and reduced delay times. The High-Performance NED can be screened to MIL-PRF-38534 Classes H & K and provides a greatly improved functional replacement for the nearly 40-year-old legacy NED solution.

## **Key Features**

- Gamma Dose Rate Sensitivity Threshold Range Adjustable from 5 x 10<sup>4</sup> to 2 x 10<sup>7</sup> rads (Si) / sec.

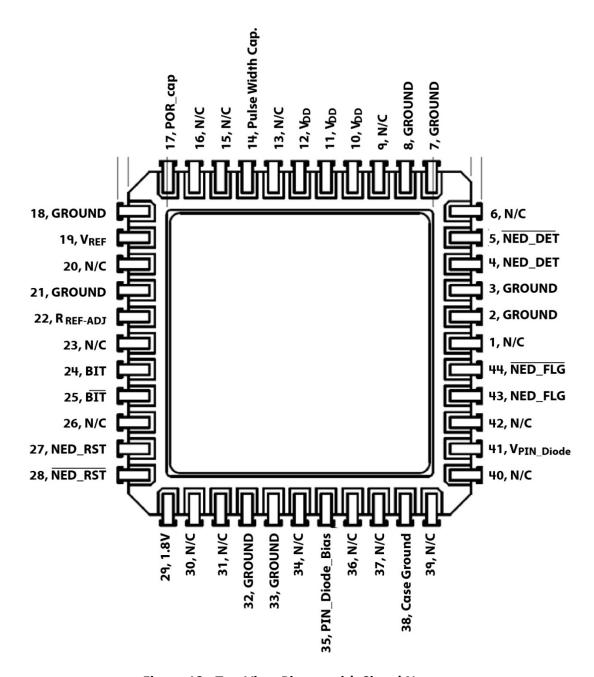

- 44-Pin Hermetic Ceramic J-Lead SMT Package (.650in x .650in x .113in)

- Integrated Differential Line Drivers and Receivers Eliminates the Need for Shielding External Drivers and Receivers

- Radiation Specifications

- o Total Dose (Device Survivability): 1 x 10<sup>6</sup> rads(Si)

- o Dose Rate (Operate Through): 1 x 10<sup>12</sup> rads(Si)/sec

- Neutron Fluence (Operate Through): 5 x 10<sup>13</sup> neutrons/cm<sup>2</sup>

- Delay from Radiation Detected to Output Signal Asserted:

15ns at 2X Overdrive

- 3.3V Power Requirement

- -55°C to +125°C Temperature Range

- MIL-PRF-38534 Classes H & K

# Benefits

- 4X Lower Minimum Dose Rate Sensitivity

- 25% Faster Response Time at 5X Lower Overdrive Level Enabling a More Rapid Shutdown of Critical Electronics

- Improved Noise Immunity

- Use Output Signal to Shut Down Power Supplies, Take

Processors Offline and Block Memory Write Operations

- US Manufactured

- Improvements in Obsolescence Mitigation with In-House PIN Diode and Controller

- Screening for Space Option Available

# **Applications**

- · Aircraft and Drones

- Defense Weapon Systems

- Satallitas

- Military Ground Vehicles

- Nuclear Material Storage

# **Revision History**

| Revision | Description                                                                                                                                                                           | Release Date |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|

| 0.1      | Initial Draft of Advanced Information Datasheet                                                                                                                                       | 08/15/2023   |  |  |

| 0.2      | Updated After Testing                                                                                                                                                                 | 03/22/2024   |  |  |

| 1.0      | Initial Release of Advanced Information Datasheet                                                                                                                                     | 04/08/2024   |  |  |

| 1.1      | Correction to Table 1, Neutron Fluence                                                                                                                                                | 04/09/2024   |  |  |

| 1.2      | Updated block diagram and outline drawing, addition of signal pinout and description table, addition of PC board pad recommended pad locations drawing and various editorial changes. | 09/26/2024   |  |  |

| 1.3      | Updated signal descriptions for pins 27 and 28, NED_RST and, to correct error in indicated signal polarity.                                                                           | 10/10/2024   |  |  |

| 1.4      | Reversed signal names for NED_DET and NED_DET signals (pins 4 and 5) and for NED_FLG and NED_FLG_L signals (pins 43 and 44).  Also, updated the descriptions for these signals.       | 10/11/2024   |  |  |

| 1.5      | Corrected errors in signal description for pins 43 and 44, NED_FLG and NED_FLG_L.                                                                                                     | 10/30/2024   |  |  |

| 1.6      | Updated outline drawing, including adding dimensional tolerances.                                                                                                                     | 2/19/2025    |  |  |

| 1.7      | Updated ordering information                                                                                                                                                          | 4/16/2025    |  |  |

| 1.8      | Updated cover and page header from part number to name; added application information                                                                                                 | 6/20/2025    |  |  |

| 1.9      | Added reference to case ground pin; BIT pulse time; graphs for R <sub>REF-</sub> ADJ and C <sub>PULSE</sub> ; added mention about delay time test.                                    | 7/24/2025    |  |  |

| 1.10     | Corrected error in signal polarities for NED_DET, NED_FLG and 1.10 NED_RST differential signals. Added package top view diagram including signal names.                               |              |  |  |

|          |                                                                                                                                                                                       |              |  |  |

## **High-Performance NED**

Form #: CSI-D-686

Document: HP-NED

### **Table of Contents**

| 1.0 | De    | scription                               | 5  |

|-----|-------|-----------------------------------------|----|

| 2.0 | Sp    | ecifications                            | e  |

| 3.0 | Op    | eration                                 | 8  |

| 3   | 3.1   | ASIC-Based Design                       | 8  |

| 3   | 3.2   | Functional Overview                     | 8  |

| 3   | 3.3   | PIN Diode                               | 9  |

| 3   | 3.4   | Detector Circuit                        | 9  |

| 3   | 3.5   | Variable Dose Rate Threshold            | 10 |

| 3   | 3.6   | Differential Line Drivers and Receivers | 10 |

| 3   | 3.7   | Differential and Single-Ended Operation | 12 |

| 3   | 3.9   | Built-In Self-Test                      | 14 |

| 3   | 3.10  | Radiation Testing                       | 14 |

| 3   | 3.11  | Pinout and Signal Descriptions          | 14 |

| 4.0 | Ар    | plication Information                   | 17 |

| 4   | 1.1   | Input Signals                           | 17 |

| 4   | 1.1.1 | Differential Inputs                     | 17 |

| 4   | 1.1.2 | Single Ended Inputs                     | 18 |

| 4   | 1.2   | Output Signals                          | 18 |

| 4   | .2.1  | Differential Outputs                    | 18 |

| 4   | .2.2  | Differential Outputs                    | 19 |

| 4   | 1.3   | Power Supply Crowbarring                | 19 |

| 4   | 1.4   | Shutting Down Processing                | 20 |

| 5.0 | Pa    | ckaging                                 | 21 |

| 6 N | Or    | dering Information                      | 25 |

# **High-Performance NED**

# **List of Figures**

| Figure 1. Nuclear Event Detector (NED) Block Diagram                          | 5  |

|-------------------------------------------------------------------------------|----|

| Figure 2. Dose Rate Threshold Adjustment Resistor                             | 11 |

| Figure 3. NED_DET (pulse), NED_FLG (latched level) and NED_RST (reset) Timing | 13 |

| Figure 4. Pulse Width Capacitor                                               | 13 |

| Figure 5. Differential Input Signal Termination                               | 17 |

| Figure 6. Single-Ended Input Signal Termination                               | 18 |

| Figure 7. Differential Output Remote Signal Terminations                      | 18 |

| Figure 8. Single-Ended Output Remote Termination                              | 19 |

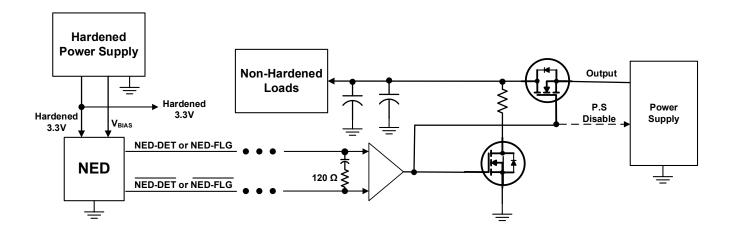

| Figure 9. Using NED Output to Activate Power Supply Crowbarring               | 20 |

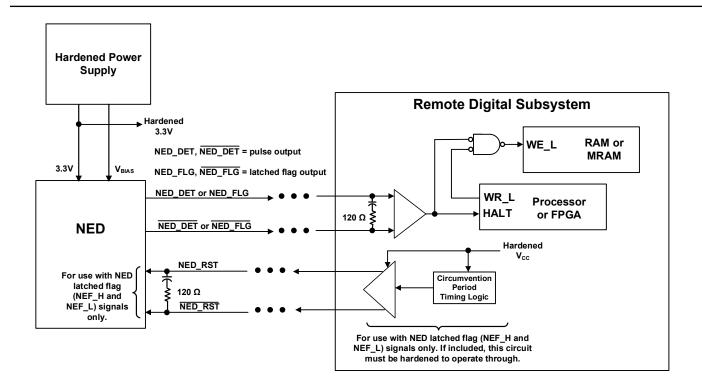

| Figure 10. NED Output Shuts Down CPU and Memory Write Operations              | 21 |

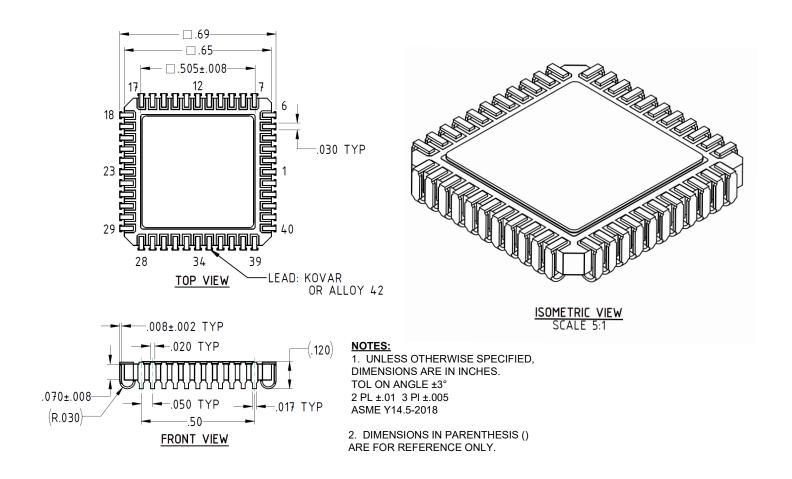

| Figure 11. 44-pin J-Lead Surface Mount Package Outline                        | 22 |

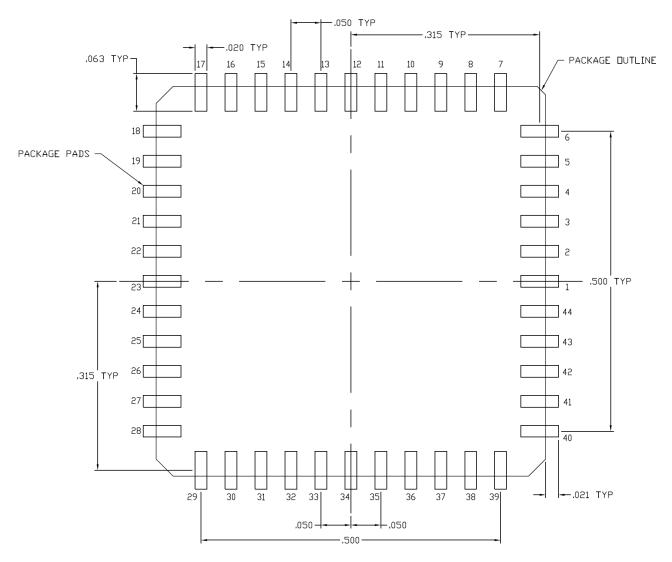

| Figure 12. Recommended PC Board Pad Placement Diagram                         | 23 |

| Figure 13. Top View Pinout with Signal Names                                  | 24 |

|                                                                               |    |

| List of Tables                                                                |    |

| Table 1. Absolute Maximum Range                                               | 6  |

| Table 2. Electrical Specs and Characterisitics                                | 6  |

| Table 3. Signal Pinout and Descriptions                                       | 14 |

| Table 4 Part Numbers                                                          | 25 |

# 1.0 Description

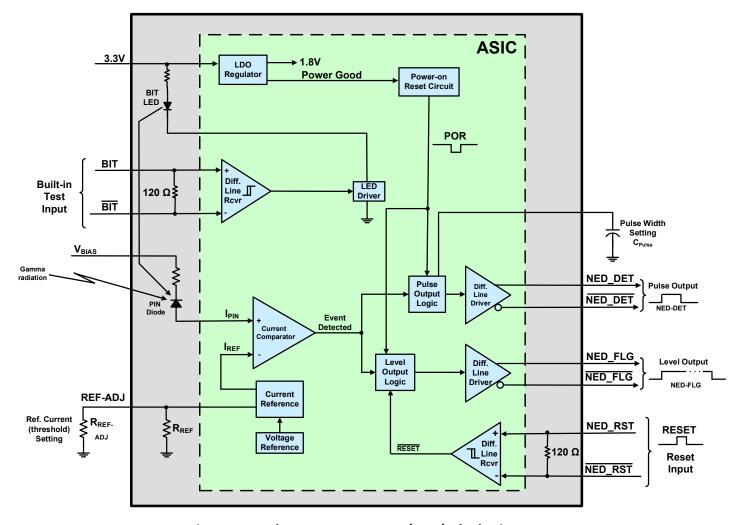

Micross' High-Performance Nuclear Event Detector (NED, Figure 1) can detect gamma radiation pulses from a nuclear event. Within 15 ns following the leading edge of an incoming gamma radiation pulse, the High-Performance NED will assert its differential pulse and level output signals. The High-Performance NED's level output may then be reset by the assertion of a differential input signal. The MYXRHNED features a minimum dose rate threshold of  $5 \times 10^4$  rads(Si)/sec, thereby providing higher sensitivity than currently available NEDs. The dose rate threshold can be increased upwards up to  $2 \times 10^7$  rads(Si)/sec, by means of an external adjustment resistor. The High-Performance NED, which is available in a 44 pin J-Lead ceramic package, is radiation hardened, enabling it to operate reliably in environments with high gamma dose and gamma dose rate, neutrons and heavy ions; and provide immunity to latch up. It achieves this by using a custom designed PIN diode that's optimized for gamma radiation, along with a rad-hard-by-design ASIC designed specifically for this purpose. Since the ASIC contains the line drivers and receivers on-board as Rad Hard blocks, no additional consideration is needed for those functions.

Figure 1. Nuclear Event Detector (NED) Block Diagram

# 2.0 Specifications

Table 1 provides the absolute maximum ratings for the MYXRHNEDHCJ/X nuclear event detector (NED), while Table 2 provides the electrical and mechanical specifications and characteristics.

| Table 1. Absolute Maximum Range     |          |                      |                          |  |  |  |

|-------------------------------------|----------|----------------------|--------------------------|--|--|--|

| Parameter                           | Min      | Max                  | Unit                     |  |  |  |

| Hardened Supply Voltage             | -0.5     | 3.6                  | V                        |  |  |  |

| PIN Diode Bias Voltage              | 0        | 100                  | V                        |  |  |  |

| Differential Receivers Line Voltage | -8.0     | 8.0                  | V                        |  |  |  |

| Differential Drivers Line Voltage   | -0.5 3.6 |                      | V                        |  |  |  |

| ESD Sensitivity                     |          | Class 2              |                          |  |  |  |

| Junction Temperature, TJ            | -55      | 150                  | °C                       |  |  |  |

| Storage Temperature Range           | -65      | 150                  | °C                       |  |  |  |

| Total Dose (Device Survivability)   |          | 1 x 10 <sup>6</sup>  | rads(Si)                 |  |  |  |

| Dose Rate (Operate Through)         |          | 1 x 10 <sup>12</sup> | rads(Si)/sec             |  |  |  |

| Neutron Fluence (Operate Through)   |          | 5 x 10 <sup>13</sup> | neutrons/cm <sup>2</sup> |  |  |  |

| SEE LET Threshold                   |          | 40                   | MeV-cm <sup>2</sup> /g   |  |  |  |

| Table 2. Electrical Specs and Characterisitics                                 |                   |                                                                     |                     |                     |              |                      |  |

|--------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------|---------------------|---------------------|--------------|----------------------|--|

| Parameter                                                                      | Symbol            | Conditions                                                          | Min                 | Max                 | Unit         | Group A<br>Subgroups |  |

| Approximate Dose Rate Detection Range                                          |                   | V <sub>BIAS</sub> = 20 volts                                        | 5 x 10 <sup>4</sup> | 2 x 10 <sup>7</sup> | Rads(Si)/sec |                      |  |

| Dose Rate Threshold Variation<br>Over Temperature                              |                   | Relative to Room Temperature<br>Threshold Over Temperature<br>Range | -20                 | +20                 | %            |                      |  |

| Hardened Power Supply Operational Voltage                                      | V <sub>CC</sub>   |                                                                     | 3.0                 | 3.6                 | V            | 1,2,3                |  |

| Hardened Power Supply Current                                                  |                   | Notes 1,2                                                           |                     |                     |              |                      |  |

| Both differential driver output circuits unterminated or AC-coupled terminated |                   | V <sub>CC</sub> = 3.3V                                              |                     | 5                   |              |                      |  |

| One differential driver output circuit DC-coupled terminated                   | I <sub>cc</sub>   |                                                                     |                     | 35                  | mA           | 1,2,3                |  |

| Both differential driver output circuits DC-coupled terminated                 |                   |                                                                     |                     | 65                  |              |                      |  |

| PIN Diode Bias Voltage                                                         | V <sub>BIAS</sub> |                                                                     | 4.5                 | 100                 | V            | 1,2,3                |  |

| Table 2. Electrical Specs and Characteristics Cont.                            |                           |                                     |                                                                |                                   |                       |                      |

|--------------------------------------------------------------------------------|---------------------------|-------------------------------------|----------------------------------------------------------------|-----------------------------------|-----------------------|----------------------|

| Parameter                                                                      | Symbol                    | Conditions                          | Min                                                            | Max                               | Unit                  | Group A<br>Subgroups |

| PIN Diode Bias Current Standby                                                 | I <sub>BIAS</sub>         |                                     |                                                                | 10                                | μΑ                    | 1,2,3                |

| Radiation Propagation Delay<br>Time to NED_DET and NED_FLG<br>outputs asserted |                           | Notes 3,4                           |                                                                |                                   |                       |                      |

| Gamma Dose Rate = 1 x 10 <sup>5</sup> rads(Si)/second                          | t <sub>D</sub>            | V <sub>BIAS</sub> = 20 Volts        |                                                                | 15                                | ns                    |                      |

| Gamma Dose Rate = 2 x 10 <sup>7</sup> rads(Si)/second                          |                           |                                     |                                                                | 7                                 | ns                    |                      |

| Differential Receivers' Voltage<br>Threshold                                   | $V_{DR}$                  | V <sub>CC</sub> = 3.3V              | -0.2                                                           | 0.2                               | $V_{PK}$              | 1,2,3                |

| Differential Receivers' Common<br>Mode Voltage Range                           | V <sub>CM</sub>           | V <sub>CC</sub> = 3.3V              | -7.0                                                           | 7.0                               | V                     | 1,2,3                |

| Differential Receivers'<br>Hysteresis Voltage                                  | V <sub>RX-HYST</sub>      | V <sub>CC</sub> = 3.3V              | 50                                                             | typ.                              | mV                    | 1,2,3                |

| Differential Line Driver<br>Differential Output Voltage                        | $V_{DT}$                  | V <sub>CC</sub> = 3.3V              | 3.0                                                            | 10.0                              | V <sub>PK-to-PK</sub> | 1,2,3                |

| Pulse Output Pulse Width Range                                                 | t <sub>PULSE</sub>        | Adjustable by External<br>Capacitor | 0.1                                                            | 10                                | ms                    |                      |

| NED-RST (RESET) Pulse Width                                                    | t <sub>RESET</sub>        |                                     | 1.0                                                            |                                   | μs                    | 9,10,11              |

| NED-RST asserted to NED_FLG de-asserted                                        | t <sub>RESET-to-FLG</sub> |                                     | 300                                                            | (typ)                             | ns                    |                      |

| BIT Pulse Width                                                                | t <sub>BIT</sub>          |                                     | 10                                                             |                                   | μs                    |                      |

| Operating Temperature Range                                                    | TOPERATION                |                                     | -55                                                            | +125                              | °C                    |                      |

| Package                                                                        |                           |                                     | Ceran                                                          | nic BGA                           |                       |                      |

| Outline Dimensions                                                             |                           |                                     |                                                                | 55 x 3.05 typ.<br>91 x 0.12) typ. | mm (in)               |                      |

| Mass (Weight)                                                                  |                           |                                     | 0.5 typ. (                                                     | 0.018 typ.)                       | g (oz)                |                      |

| Lot Qualification and Acceptance Testing                                       |                           |                                     | XT, or in accordance with MIL-PRF-<br>38534 Class H or Class K |                                   |                       |                      |

#### **Notes:**

- 1. The max. values for ICC assume the dose rate threshold is set to its minimum value of 5 x  $10^4$  rads(Si)/sec. For the external adjustment threshold resistor selected for the maximum dose rate threshold of 2 x  $10^7$  rads(Si)/sec, the max. value of ICC increases by 7 mA. Refer to section 3.5.

- 2. For the NED and NEF line drivers, the termination loads on the line drivers are assumed to be 120 ohms differential (resistive). The use of RC terminations will reduce NED power consumption and dissipation accordingly.

- 3. Dose rate threshold is set to its minimum value of 5 x 10<sup>4</sup> rads(Si)/sec.

- 4. Delay time  $t_D$  is defined as the time between the 50% point of the rising edge of the incoming gamma radiation pulse to the 50% point of the high-to-low voltage transition for the NED and NEF differential output signals.

- 5. Micross also has data indicating that the detection time of the NED's custom PIN diode is approximately 40 nS faster than "industry standard" parts such as the UM9441.

# 3.0 Operation

#### 3.1 ASIC-Based Design

Micross' ASIC-based design provides multiple benefits relative to legacy nuclear event detectors:

- 1. It enables construction of a NED in a smaller and lighter package, capable of surviving prompt dose radiation.

- 2. Inclusion of differential drivers on chip improves overall response time, while legacy products suffer further response time degradation when external drivers are added.

- 3. By greatly reducing the number of components, wire bonds and interconnects, the Micross NEDs' reliability (MTBF) will be significantly higher than that of other NEDs.

- 4. Use of sub-micron ASIC technology and operation from lower power supply voltages will reduce the NED's power consumption and dissipation.

- 5. As a means of mitigating against obsolescence, Micross is not dependent on third-party suppliers for key components.

- 6. Micross' selected trusted foundry is on-shore and offers a 180 nm process with the capability to produce chips that meet the NED's radiation requirements. These requirements are:

- Total gamma dose: 300 krads (Si), with a goal of 1 Mrads (Si)

- Gamma dose rate (operate-through): 1 x 10<sup>12</sup> rads(Si)/sec

- Neutron fluence (operate-through): 10<sup>13</sup> n/cm<sup>2</sup>

#### 3.2 Functional Overview

As shown in Figure 1, the MYXRHNEDHCJ/X NED includes a 3.3V-to-1.8V LDO regulator. With the exception of the PIN diode and the two differential line drivers, all circuitry in the NED is powered by the ASIC's 1.8V supply rail. The two differential line drivers are powered directly by the 3.3V input power.

The NED includes a PIN diode to sense incoming gamma radiation from a nuclear explosion. Gamma radiation will result in current flowing through the reverse-biased PIN diode into the "+" side of a current comparator.

The input to the "-" side of the current comparator is provided by a reference circuit. This reference current is user-adjustable by means of the external resistor  $R_{REF-ADJ}$  (see Figure 1 and section 3.5). As explained in section 3.5, installing a lower value for  $R_{REF-ADJ}$  will increase the value of the reference current and as a result, increase the value of the NED's dose rate threshold.

When the PIN diode current exceeds the reference current, the output state of the comparator will assert active, indicating that a nuclear event has been detected.

Following power turn-on, when the 1.8V regulator senses that its output has exceeded a voltage of approximately 1.0 volt, it will assert its POWER GOOD output signal. This will result in the generation of a

negative-going "POR" (power-on reset) pulse. This pulse will reset the NED's two differential outputs NED and NEF to their quiescent (inactive) states of logic "1". Once this occurs, the NED and NEF outputs will remain in their de-asserted states (high) until a nuclear event is detected.

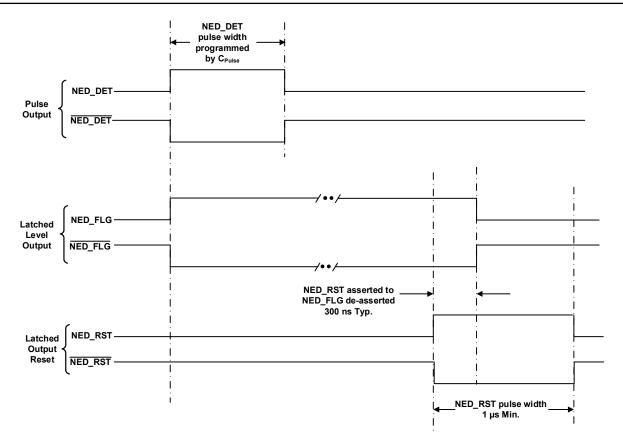

Following the detection of a nuclear event, NED-DET and NED-FLG will transition from their quiescent, deasserted states of logic "0" (low) to their active, asserted states of logic "1" (high). The NED-DET pulse output will assert low for a fixed amount of time, as determined by the value of an external capacitor (see Figure 1 and section 3.8). The NED-FLG (latched flag) output will remain asserted until the receipt of a negative going pulse on the RESET differential input. A logic "1" pulse on the RESET input of duration 1.0 µs or more will clear the NED FLG output back to its de-asserted state.

#### 3.3 PIN Diode

Similar to most existing NED designs, the sensing element in Micross' Nuclear Event Detector is a PIN diode. Most commercially available PIN diodes targeted to sensing applications are designed to operate at longer wavelengths, such as RF, visible, infrared, ultraviolet and X-ray. In particular, they're not designed to be optimized for detecting gamma radiation. For use in its NED, Micross has designed and fabricated its own PIN diode that's optimized for detecting gamma radiation. This internal development and captive manufacturing will ensure Micross with a reliable supply of PIN diodes, providing very strong mitigation against future obsolescence.

For its PIN diode development, Micross Components focused on the goals of wide dynamic range and fast response time in response to short duration pulses of gamma radiation. The PIN diode development involved extensive testing and characterization of the PIN diode in a flash X-ray facility.

To provide a reverse bias voltage to the NED's PIN diode, it's highly recommended to apply a minimum voltage of +15V to the PIN\_Diode\_Bias input ( $V_{BIAS}$ ). Although it's possible to operate the NED from a lower value of  $V_{BIAS}$ , this will reduce the NED's sensitivity and therefore increase its dose rate threshold. It's also possible to reduce the NED's minimum dose threshold level and response time to a nuclear event by increasing the value of this voltage above 15V.

In the case of a nuclear event, the PIN diode current can spike to very high levels depending on the radiation level. To provide protection, the NED includes a 2.5 k $\Omega$  current-limiting resistor in series with the PIN diode. For a worst case scenario and assuming  $V_{BIAS}$  = 15V, the maximum reverse bias current that would flow through the NED = 15V/ 2.5 k $\Omega$  = 6 mA.

#### 3.4 Detector Circuit

In addition to the PIN diode, the most critical functional block of the NED is its detector circuit. For this function, Micross includes a current comparator circuit in its NED ASIC. In contrast to the voltage comparator used in legacy NEDs, Micross' use of a current comparator provides better speed performance by minimizing the impedance seen by the detector. This minimizes the value and effect of the circuit's inherent RC time constant.

The detector circuit includes a reference current circuit. The reference circuit provides a DC current output based on the input from a precision voltage source. To allow users to set the value of the NED's dose rate threshold, the reference current and therefore the dose rate threshold is programmable by means of an external resistor. The reference current circuit includes temperature compensation to offset temperature-dependent variations in the PIN diode and the current comparator. One of the goals for the detector's current

comparator circuit is to provide very fast detection speed that's largely independent of the NED's threshold sensitivity setting.

Based on the use of a custom PIN diode and the inherent advantages of a current comparator, the MYXRHNEDHCJ/X provides superior performance for minimum dose rate threshold and delay time performance. The MYXRHNEDHCJ/X provides a minimum dose rate threshold of to  $5 \times 10^4 \, \text{rads}(\text{Si})/\text{sec}$  or lower. The major benefit of this is to detect the fast-rising edge of the nuclear event sooner and to reduce the number of false negatives.

Relative to other NEDs, the MYXRHNEDHCJ/X also provides a significant improvement for the overall delay time between the leading edge of a gamma radiation pulse and the assertion of its output signal. The MYXRHNEDHCJ/X will reduce the value of this internal time delay to 15 ns with an overdrive ratio of 2. For users, NED delay time is a critical parameter, since shorter delays enable improved protection of other on-board electronic circuitry.

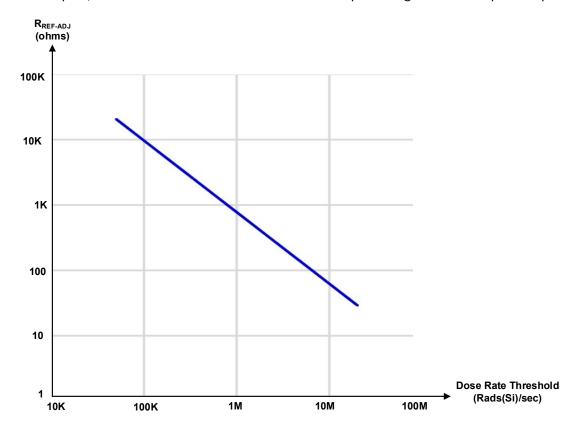

#### 3.5 Variable Dose Rate Threshold

As shown in Figure 1, the NED provides a means to program the value of its dose rate threshold. This is done by connecting a resistor designated as  $R_{REF-ADJ}$  between the signal  $R_{REF-ADJ}$  and GROUND. If no resistor is connected between  $R_{EF-ADJ}$  and GROUND, the dose rate threshold defaults to its minimum value of approximately 5 x  $10^4$  rad(Si)/sec. To configure the NED for a higher value of dose rate threshold, it's necessary to connect an external resistor between  $R_{REF-ADJ}$  and GROUND.

To program for a value of dose rate threshold = DRT, the value of the external resistor should be:

$$R_{REF-ADJ} = \frac{2.9E9}{DRT^{1.0961}}$$

For example, to configure the NED for a dose rate threshold of 5 x 10<sup>5</sup> rad(Si)/sec, the value of the external resistor should be:

$$R_{REF-ADJ} = \frac{2.9E9}{(500,000)^{1.0961}} = 1,643 \Omega$$

The graph of Figure 2 shows the relationship between dose rate threshold and the value of the adjustment resistor.

#### 3.6 Differential Line Drivers and Receivers

As shown in Figure 1, the MYXRHNEDHCJ/X includes differential line drivers and receivers for the various digital output and input signals. It includes differential drivers for the NED pulse output and NEF level output, and differential receivers for the RESET and BIT input signals.

Differential drivers and receivers provide improved signal integrity, noise rejection and common mode rejection relative to single-ended divers and receivers, especially single-ended drivers consisting of open-collector or open-drain circuits. Micross designed the differential drivers and receivers to provide reliable operation in the presence of the types of noise transients that occur during nearby nuclear events. To lessen the effects of noise, the receivers include built-in circuit protection, hysteresis and common mode rejection. The NED's differential

drivers and receivers are designed to meet or exceed the requirements of the EIA RS-422 standard. For the transmitter outputs, this will include a minimum differential output voltage of 3.0 volts peak-to-peak.

Figure 2. Dose Rate Threshold Adjustment Resistor

The differential receiver for the RESET input will be biased to provide a logic "1" (inactive) output when there's no incoming signal, while the differential receiver for the BIT (Built-in Test) input will be biased to provide a logic "0" (inactive) output when there's no incoming signal. In addition, the differential receivers will include positive and negative threshold voltages of less than ±0.2 V peak, provide a minimum hysteresis voltage of 50 mV and operate with common mode voltages equal to or greater than the range of -7V to +7V.

The external signals for the differential and single-ended line drivers and receivers will include clamping diodes to  $V_{CC}$  and GROUND to protect against electrostatic discharge (ESD).

The delays through the MYXRHNEDHCJ/X's on-ASIC differential line drivers are approximately 5 ns. Note that other NEDs provide single-ended open-collector drivers rather than differential drivers. In order to gain the benefit of differential signaling using these NEDs, it's necessary to use external differential drivers. For the MYXRHNEDHCJ/X, the inclusion of the internal differential drivers provides a large speed improvement over the use of external drivers, which add additional delays of approximately 15 ns.

To ensure reliable operation of the NED\_H and NED\_L differential pulse type output and/or the NEF\_H and NEF\_L differential level type output, it's necessary to terminate the end of the differential cable going into a differential receiving circuit with a resistor that matches the cable's differential characteristic impedance. For

signals adhering to the RS-422 standard, the standard value for the cable characteristic impedance and terminating resistance is 120 ohms.

#### 3.7 Differential and Single-Ended Operation

The NED's BIT and RESET inputs, and NED\_DET and NED\_FLG outputs can be operated as either differential pairs or as single-ended signals. As shown in Figure 1, to operate the BIT and/or RESET inputs in differential mode, it's recommended to connect a 120 ohm termination resistor between BIT and  $\overline{\rm BIT}$  or between NED\_RESET and  $\overline{\rm NED}$  RST.

To operate these inputs in single-ended mode, it is recommended to connect a termination resistor between the used input signal (e.g., BIT) and GROUND and to connect the unused input (e.g.,  $\overline{\text{BIT}}$ ) to a voltage of approximately 0.5\*  $V_{DD}$  through a simple resistive voltage divider.

Similarly, the NED's NED\_DET and NED\_FLG output signals can also be operated as either differential pairs or as single-ended signals. When operating NED\_DET and NED\_DET and/or NED\_FLG and NED\_FLG in differential mode, it's recommended to connect a termination resistor across the receiving end of the differential link. The value of this resistor should match the characteristic impedance of the interconnecting cable. For RS-422 type signals, cables with 120 ohm impedance are commonly used. To use these output signals in single-ended mode, it is recommended to connect a termination resistor (e.g., 120 ohms) between the used signal conductor (e.g., NED\_H) and GROUND at the receiving end of the signal link.

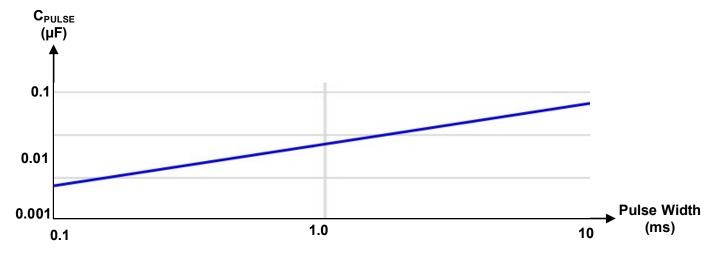

## 3.8 NED\_H/NED\_DET Pulse Width Setting

To program the pulse width duration from the NED\_DET/NED\_DET differential output, connect a capacitor between the signal Pulse Width Cap. and ground. The value of this capacitor should be:

Cap value =

$$\frac{\text{Pulse (sec)}}{16,000}$$

For example, for a pulse width =  $100 \mu s$ ,

Cap value

$$= \frac{0.0001}{16,000} = 6.25 \text{ nF}$$

The graph of Figure 4 shows the relationship between desired output pulse width and the value of the capacitor.

Figure 3. NED\_DET (pulse), NED\_FLG (latched level) and NED\_RST (reset) Timing

Figure 4. Pulse Width Capacitor

#### 3.9 Built-In Self-Test

To enable Built-in self-test (BIT), the MYXRHNEDHCJ/X includes an LED. This LED will be controlled by the BIT (built-in test) differential input signal. When BIT is asserted to logic "1", the LED will illuminate the PIN diode. During this test if the NED-DET and NED-FLG output signals assert high, the self-test will be considered to have passed. However, if the NED-DET and NED-FLG signals remain inactive, this indicates that the has failed. To ensure that the NED-DET pulse output and NED-FLG latched level output assert during self-test, the differential BIT signal should be asserted for at least 10  $\mu$ s.

#### 3.10 Radiation Testing

Each MYXRHNEDHCJ/X NED shipped will be tested for a dose rate threshold of approximately  $5 \times 10^4$  rads(Si)/sec, the specified minimum value, and a radiation-to-output assertion time of approximately 15 ns at 2x overdive.

#### 3.11 Pinout and Signal Descriptions

Table 3 provides the pinout and signal descriptions for the NED.

|               | Table 3. Signal Pinout and Descriptions |                    |                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|---------------|-----------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>Number | Signal Name                             | Input or<br>Output | Description                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1             | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                               |  |  |  |

| 2             | GROUND                                  |                    | GROUND                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3             | GROUND                                  |                    | GROUND                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 4             | NED_DET                                 | Output             | NED differential pulse output. Quiescently, NED_DET outputs a low                                                                                                                                                                                                                                                                               |  |  |  |

| 5             | NED_ DET                                | Output             | level and NED_DET outputs a high level. When the NED detects a nuclear event, NED_DET transitions to a high level and NED_DET transitions to a low level for the programmed duration of the pulse output. The length of the pulse is determined by the value of the external pulse width control capacitor connected between pin 14 and GROUND. |  |  |  |

| 6             | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                               |  |  |  |

| 7             | GROUND                                  |                    | GROUND                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 8             | GROUND                                  |                    | GROUND                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 9             | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                               |  |  |  |

| 10            | $V_{DD}$                                | Input              | 3.3V power input                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 11            | $V_{DD}$                                | Input              | 3.3V power input                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 12            | $V_{DD}$                                | Input              | 3.3V power input                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 13            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                               |  |  |  |

| 14            | Pulse Width Cap.                        |                    | As described in section 3.8, the duration of the NED's pulse type output asserted by the differential pair NED_DET and NED_DET                                                                                                                                                                                                                  |  |  |  |

|               | Table 3. Signal Pinout and Descriptions |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------------|-----------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>Number | Signal Name   '   Description           |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|               |                                         |       | needs to be configured by connecting a capacitor between Pulse Width Cap. and GROUND.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 15            | N/C                                     |       | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 16            | N/C                                     |       | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 17            | POR_cap                                 |       | This pin may be left unconnected. However, it may be used to increase the NED's power-on reset time. To do that, connect an external capacitor between POR_cap and GROUND.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 18            | GROUND                                  |       | GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 19            | $V_{REF}$                               |       | Connects to internal reference voltage used for current comparator circuit. Do <u>not</u> connect to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 20            | N/C                                     |       | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 21            | GROUND                                  |       | GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 22            | R <sub>REF-ADJ</sub>                    |       | External resistor to adjust the NED dose rate threshold. To configure the NED for its minimum dose rate threshold of 5 x 10 <sup>4</sup> rad(Si)/sec, this pin should be left open. As described in section 3.5, the NED's dose rate threshold can be adjusted to a higher value by connecting a resistor between R <sub>REF-ADJ</sub> and GROUND.                                                                                                                                                                                             |  |  |  |

| 23            | N/C                                     |       | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 24            | BIT                                     | Input | Differential Built-in Test (BIT) input. To perform the NED's built-in                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 25            | BIT                                     | Input | test, this differential signal should be asserted with BIT driven high relative to $\overline{BIT}$ . To determine if the NED has passed its built-in test, verify that the NED_DET/ $\overline{NED}$ _DET pulses for the period programmed by the Pulse Width Cap. and that NED_FLG/ $\overline{NED}$ _FLG asserts its latched level output until NED_RST (RESET) is asserted. To ensure that the NED_DET pulse and NED_FLG latched outputs assert during self-test, the differential BIT signal should be asserted for at least 10 $\mu s$ . |  |  |  |

| 26            | N/C                                     |       | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 27            | NED_RST                                 | Input | Differential NED Reset input. For normal operation, NED_RST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 28            | NED_RST                                 | Input | should be asserted low and $\overline{NED\_RST}$ should be asserted high. Following detection of a nuclear event, the NED_FLG/ $\overline{NED\_FLG}$ latched differential level output will assert. To clear the NED_FLG/ $\overline{NED\_FLG}$ output, it's necessary to assert the NED_RST input. This is done by driving NED_RST high and $\overline{NED\_RST}$ low for a minimum time of 1.0 $\mu$ s.                                                                                                                                      |  |  |  |

|               | Table 3. Signal Pinout and Descriptions |                    |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|---------------|-----------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin<br>Number | Signal Name                             | Input or<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|               |                                         |                    | <ol> <li>If the NED_RST/NED_RST input is asserted, this will prevent the NED_FLG/NED_FLG output from asserting.</li> <li>The NED_RST/NED_RST input has <u>no</u> effect on the NED_DET/NED_DET pulse output.</li> </ol>                                                                                                                                                                                    |  |  |  |  |

| 29            | 1.8V                                    | Input              | Internal 1.8V output. Do <u>not</u> connect to this pin.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 30            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 31            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 32            | GROUND                                  |                    | GROUND                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 33            | GROUND                                  |                    | GROUND                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 34            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 35            | PIN_Diode_Bias                          | Input              | PIN Diode Bias. To provide a reverse bias voltage to the NED's PIN diode, it's necessary to apply a minimum voltage of +15V to the PIN_Diode_Bias input. It's possible to reduce the NED's response time to a nuclear event by increasing the value of this voltage.                                                                                                                                       |  |  |  |  |

| 36            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 37            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 38            | Case Ground                             |                    | Case ground. It is recommended to connect this pin to chassis ground.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 39            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 40            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 41            | $V_{PIN\_Diode}$                        |                    | Internal connection to a resistor that connects between the PIN diode and the ASIC. Do <u>not</u> connect to this pin.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 42            | N/C                                     |                    | No internal connection. Should connect to ground.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 43            | NED_FLG                                 |                    | NED latched flag output. Quiescently, NED_FLG outputs a low level                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 44            | NED_FLG                                 | Output             | and $\overline{NED\_FLG}$ outputs a high level. When the NED detects a nuclear event, NED_FLG transitions to a high level and $\overline{NED\_FLG}$ transitions to a low level. The state of this differential output signal is internally latched and the output remains asserted until the NED_RST input is asserted by driving NED_RST high and $\overline{NED\_RST}$ low for a minimum of 1.0 $\mu$ s. |  |  |  |  |

# 4.0 Application Information

#### 4.1 Input Signals

The NED includes two pairs of differential input signals: the NED\_RST and  $\overline{NED}$ \_RST (RESET) inputs for resetting the flag (level type) output signal and the BIT and  $\overline{BIT}$  inputs for activating built-in test. These signals may be operated as either differential pairs or as single-ended signals.

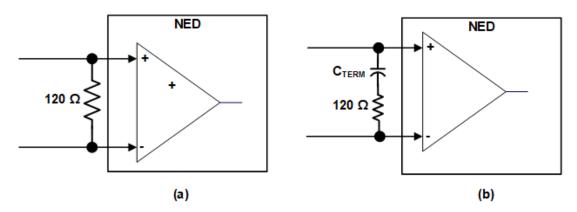

#### 4.1.1 Differential Inputs

For operating the RESET and BIT signals as differential pairs, the signal pairs should be terminated with 120 ohm resistors as shown in Figure 5. To reduce power dissipation by the differential drivers from an external circuit, it's recommended to include a capacitor ( $C_{\text{TERM}}$ ) in series with the termination resistor, as shown in Figure 5(b). This prevents the need for the driving circuit to provide current except during signal transitions between its high and low states. To minimize reflections, it's recommended that the RC time constant of the series RC termination be much greater than the anticipated signal rise and fall times. For example, an 0.01  $\mu$ F capacitor will provide a time constant of 12  $\mu$ s, much longer than the incoming signals' maximum anticipated rise and fall times.

Figure 5. Differential Input Signal Termination

(a) Simple Termination; (b) AC-Coupled Termination

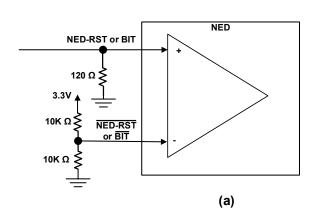

As shown in Figure 6, the NED's BIT and RESET input signals can be operated as single-ended inputs. This requires that a reference voltage of approximately  $V_{CC}/2 = 1.65V$  be applied to the NED's  $\overline{BIT}$  or  $\overline{NED_RST}$  input signal. In order to minimize power consumption for the driving circuit, similar to the circuit for differential input signals, it's recommended to include a series capacitor in series with the termination resistor, as shown in Figure 5(b). To minimize reflections, it's recommended that the RC time constant of the series RC termination be approximately equal to or greater than the anticipated pulse width. For example, an 0.1  $\mu$ F capacitor will provide a time constant of 12  $\mu$ s, much longer than the maximum anticipated rise and fall times.

#### 4.1.2 Single Ended Inputs

Figure 6. Single-Ended Input Signal Termination (a) Simple Termination; (b) AC-Coupled Termination

#### 4.2 Output Signals

The NED includes two pairs of differential output signals: NED\_DET and  $\overline{NED}$ \_DET, which provide a differential pulse output that asserts following detection of a nuclear event; and NED\_FLG and  $\overline{NED}$ \_FLG, which provide a latched flag differential output that also asserts following detection of a nuclear event. For the case of NED\_FLG and  $\overline{NED}$ \_FLG, the latched flag output is de-asserted following reception of a minimum 1.0  $\mu$ s pulse to the NED\_RST and  $\overline{NED}$ \_RST differential RESET input.

Like the NED's input signals, its differential outputs may also be operated as single-ended signals.

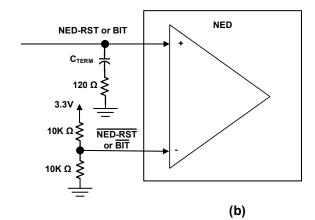

#### 4.2.1 Differential Outputs

For operating the NED\_DET and NED FLG outputs as differential pairs, the signal pairs should be remotely terminated with 120ohm resistors as shown in Figure 7. To reduce power consumption and dissipation by the NED's differential drivers, it's recommended to include a capacitor (C<sub>TERM</sub>) in series with the termination resistor, as shown in Figure 7(b). This prevents the need for the NED drivers to supply current except during signal transitions between their high and low output states. To minimize reflections, it's recommended that the RC time constant of the series RC termination be approximately equal to or greater than the anticipated pulse width.

Figure 7. Differential Output Remote Signal Terminations (a) Simple Termination; (b) AC-Coupled Termination

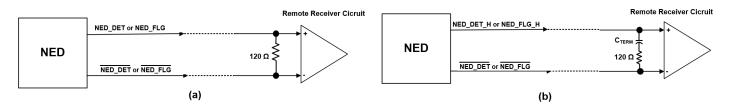

#### 4.2.2 Differential Outputs

As shown in Figure 8, the NED's NED DETECT and NED FLAG output signals can be operated as single-ended outputs. This calls for a 120ohm termination between the signal and ground at the remote receiver circuit. In order to minimize power consumption for the NED driver, similar to the circuit for differential output signals, it's recommended to includes a series capacitor in series with the termination resistor, as shown in Figure 8(b).

Figure 8. Single-Ended Output Remote Termination (a) Simple Termination; (b) AC-Coupled Termination

#### 4.3 Power Supply Crowbarring

One of the primary functions of the NED is to protect non-radiation hardened electronics from the effects of prompt dose radiation following a nuclear event. As shown in Figure 6, this involves using the NED output signal to activate a crowbar circuit to remove power from non-hardened circuits.

In Figure 6, the NED and crowbar circuit are powered by a hardened power supply. This is necessary to ensure that power for the NED itself and the crowbar circuit are able to operate through a nuclear event and the ensuing circumvention period by maintaining its output voltage.

Either the NED's pulse output (NED\_DET/NED\_ DET) or latched flag output (NED\_FLG/NED\_FLG) may be used for activating the power supply crowbar circuit. The pulse output provides a fixed duration time period to remove power from non-hardened loads, while the latched flag output requires a hardened processor, FPGA other circuit to deactivate the crowbar and restore power to non-hardened loads.

The crowbar circuits themselves must be built using radiation hardened components. In the example shown in Figure 9, the crowbar circuit operates by simultaneously disconnecting the power supply and providing a rapid discharge path to ground for decoupling capacitors for power voltages for non-hardened load circuits. If the power supply includes a digital disable input, the signal from the NED should be connected to it as shown. The resistor in series with the MOSFET connecting to ground limits the current when discharging large capacitors on the power supply output.

Figure 9. Using NED Output to Activate Power Supply Crowbarring

#### 4.4 Shutting Down Processing

In addition to removing power from non-hardened electronics, another function of NEDs is to shut down digital processing following the detection of an event. As shown in Figure 10, this is done by connecting the NED's pulse or latched flag output to the input of a remote digital subsystem. As shown in this example, following the NED's detection of a nuclear event, the processing by a CPU or FPGA processor will be temporarily halted. In addition, this circuit includes a provision to prevent writing corrupt data to RAM or MRAM memory during the circumvention period.

If the NED\_H and NED\_L (pulse output) signals are used, the circumvention period is defined by the width of the NED\_H/ NED\_L pulse. This period is user-programmable by the selection of the PULSE WIDTH CAP (Figure 1 and Figure 3) connected between the NED's pin 14 and ground. If the NEF\_H and NEF\_L (NED latched flag outputs) are used, then it will be necessary to assert the NED RESET signal at the end of the circumvention period. The circumvention period timing logic shown in Figure 9 will need to be hardened in order to operate reliably through the shut-down period for the processor and memory write logic.

Figure 10. NED Output Shuts Down CPU and Memory Write Operations

# **5.0 Packaging**

For the MYXRHNEDHCJ/X, the package size is a 17.53 x 17.53 x 3.05 mm (0.690 x 0.690 x 0.12 in.), a 44-pin J-lead surface mount ceramic package. Figure 11 is the package outline drawing, while Figure 12 is the recommended PC board pad placement diagram. Figure 13 provides the package top view pinout, including the signal names.

Figure 11. 44-pin J-Lead Surface Mount Package Outline

Figure 12. Recommended PC Board Pad Placement Diagram

Figure 13. Top View Pinout with Signal Names

# **6.0 Ordering Information**

| Table 4. Part Numbers |                                                                                                    |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Part Number           | Description                                                                                        |  |  |  |  |

| MYXRHNEDHCJ/XT        | Extended temperature (-55 to +125 °C), High Performance, Hermetic                                  |  |  |  |  |

| IVIVXRHNEDH( I/K      | Extended temperature (-55 to +125 °C), High Performance, Hermetic, MIL-PRF-38534 Class K qualified |  |  |  |  |

#### Disclaimer:

The information in this Preliminary Data Sheet is believed to be accurate; however, no responsibility is assumed by Micross Hi-Rel Components for its use, and no license or rights are granted by implication or otherwise in connection therewith. Specifications are subject to change without notice. Further, although Micross is currently able to supply small quantities of this product to interested customers, the product described herein has not yet been qualified in accordance with MIL-PRF-38534. For production, Micross plans on offering versions of the product with Class H or Class K qualification in compliance with MIL-PRF-38534.